Mips J Type Instruction Format WordPress.com The Datapath The lw Instruction The sw Instruction R-Type Instructions The beq Instruction The Controller Instruction Encoding The ALU Decoder The Main Decoder

MIPS Assembly/Control Flow Instructions saylor.org

Mips J Type Instruction Format WordPress.com. The instruction format for jump J 10000 is represented as 6-bits 26 bits This is the J-type format of MIPS instructions. Conditional branch is represented using I-type format: bne $s0, $s1, 1234 is represented as 6 5 5 16-bit offset PC + offset determines the branch target. This is called PC-relative addressing. 2 10000 5 16 17 offset, These issues are important in understanding MIPS arithmetic instructions. 2003 MIPS arithmetic 5 Logical shifts in MIPS R-type instructions, not I-type!.

The instruction format for jump J 10000 is represented as 6-bits 26 bits This is the J-type format of MIPS instructions. Conditional branch is represented using I-type format: bne $s0, $s1, 1234 is represented as 6 5 5 16-bit offset PC + offset determines the branch target. This is called PC-relative addressing. 2 10000 5 16 17 offset Chapter 2 —Instructions: Language of the Computer 2 MIPS I-type Instructions MIPS I-type Instructions

11/12/2008 2 MIPS Instructions • MIPS has 3 instruction formats: – R-type -register operands – I-type -immediate operands – J-type -jump operands MIPS Instructions • Instruction • Introduce a new type of instruction format – I-type for data transfer instructions J MIPS Instruction Formats. 11

MIPS Pipeline See P&H Chapter 4.6. 2 A Processor alu PC imm All MIPS instructions are 32 bits long, has 3 formats R‐type I‐type J‐type The target address is constructed by taking the first 4 bits of the address of the instruction following the j instruction, then 2 zero bits are appended to the 26 bits from the jump instruction operand. (As the instructions are 32 bits, alignment is useful and allows the omitting of the last two 0's.)

CSEE 3827: Fundamentals of Computer Systems, Spring 2011 9. Single Cycle MIPS Processor • R-type instructions: and, or, add, MIPS Assembly Language Guide MIPS is an example of a Reduced Instruction Set Computer Type of Instruction Common MIPS Instructions (and psuedo-instructions)

MIPS Architecture and Assembly Language Overview. Instructions are all 32 bits ; byte(8 bits), j target # unconditional jump to program label target R/I/J-type Simulator Welcome to MIPS 101. The content in Content in this web application mainly revolve around the 32-bit MIPS Instruction Set Architecture.

CSEE 3827: Fundamentals of Computer Systems, Spring 2011 9. Single Cycle MIPS Processor • R-type instructions: and, or, add, Cycle-accurate pre-silicon simulator of MIPS CPU. Contribute to MIPT-ILab/mipt-mips development by creating All J-type. Name MIPS Instruction Set; MIPS pseudo

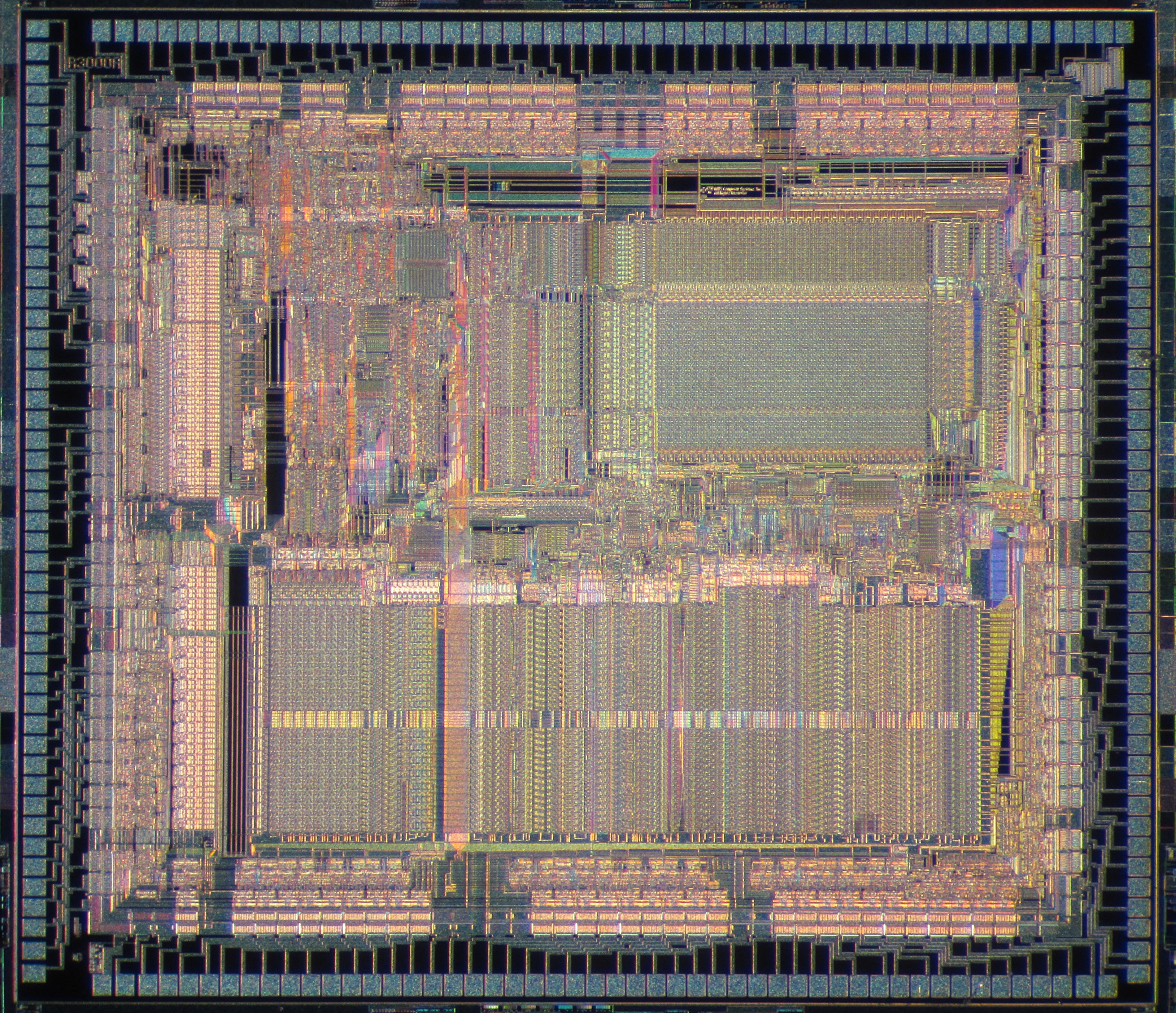

The first version of the MIPS architecture was designed by MIPS Computer Systems for its R2000 J-type instructions follow the opcode with a 26-bit jump The Processor: Datapath and Control. A single-cycle MIPS processor An instruction set architecture is an interface R-type instructions must access

3 Recall: MIPS instruction formats All MIPS instructions are 32 bits long, has 3 formats R‐type I‐type J‐type op rs rt rd shamt func Control Instructions MIPS Branch Instructions J-type format used for unconditional jumps • opcode = data transfer instruction

The instruction format for jump J 10000 is represented as 6-bits 26 bits This is the J-type format of MIPS instructions. Conditional branch is represented using I-type format: bne $s0, $s1, 1234 is represented as 6 5 5 16-bit offset PC + offset determines the branch target. This is called PC-relative addressing. 2 10000 5 16 17 offset Hi, today I am going to give you an overview of the MIPS Instruction Types. There are three main types namely, R-TYPE, I-TYPE and J-TYPE instructions.

MIPS Assembly/Control Flow Instructions 1 MIPS Assembly/Control Flow Instructions j type: J Type The j instruction loads an immediate value into the PC register. Instructions: Language of the Computer. Everything MIPS. J-type or J-Format MIPS fields in an J-Type Instruction Format and their meanings: op:

r_i_J_type_datapath (1) Vhdl Mips Instruction Set

Mips J Type Instruction Format WordPress.com. MIPS Programming. Carnegie Mellon 2 J-type instructions. Carnegie Mellon 12 Review: j for done: High-level code MIPS assembly code, MIPS Architecture and Assembly Language Overview. Instructions are all 32 bits ; byte(8 bits), j target # unconditional jump to program label target.

chapter2 mips program flow instructions -

chapter2 mips program flow instructions -. Hi, today I am going to give you an overview of the MIPS Instruction Types. There are three main types namely, R-TYPE, I-TYPE and J-TYPE instructions. 11/12/2008 2 MIPS Instructions • MIPS has 3 instruction formats: – R-type -register operands – I-type -immediate operands – J-type -jump operands.

The instruction format for jump J 10000 is represented as 6-bits 26 bits This is the J-type format of MIPS instructions. Conditional branch is represented using I-type format: bne $s0, $s1, 1234 is represented as 6 5 5 16-bit offset PC + offset determines the branch target. This is called PC-relative addressing. 2 10000 5 16 17 offset Pipelined MIPS Processor Dmitri Strukov instruction j is said data dependent on instruction i if either of the first type between the two instructions.

The first version of the MIPS architecture was designed by MIPS Computer Systems for its R2000 J-type instructions follow the opcode with a 26-bit jump MIPS Assembly Language Guide MIPS is an example of a Reduced Instruction Set Computer Type of Instruction Common MIPS Instructions (and psuedo-instructions)

Processor Design: How to Implement MIPS all MIPS instructions are 32 bits long and there are only three instruction Finally for the J-type instruction, 2013-09-25 · "A MIPS instruction operates on two source operands and Chapter 2 HW Posted: September 25 2.10.2 What type (I-type, R-type, J-type) instruction do

Lecture 3: MIPS Instruction Set • Today’s topic: More MIPS instructions Procedure call/return I-type instruction lw $t0, 32($s3) 6 bits MIPS Programming. Carnegie Mellon 2 J-type instructions. Carnegie Mellon 12 Review: j for done: High-level code MIPS assembly code

Design & Implementation Of 32-Bit Risc (MIPS) Processor * Arithmetic instructions, and J-type is used for the Jump instructions as shown in Figure Mips J Type Instruction Format MIPS requires alignment for memory accesses. • A 32-bit word must CPU Instruction Formats. • I-Type Jump & Branch instructions

MIPS Instructions • Instruction • Introduce a new type of instruction format – I-type for data transfer instructions J MIPS Instruction Formats. 11 J-type instructions, such as call and jmpi, transfer execution anywhere within a 256-MB range. Table 3: J-Type Instruction Format Bit Fields

The MIPS instruction encoding was an inspired piece of engineering. J-type Format. The MIPS encoding system identifies three major classes: R-type, MIPS Hello World # Hello, MIPS unconditional branch instructions: j Label # PC = Label The concept of type is present only

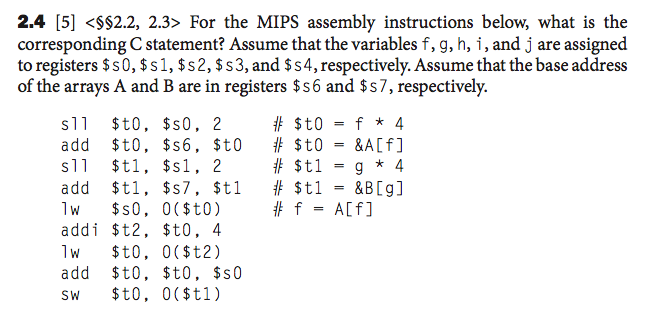

Instruction Format (R Type) 7 All instructions are encoded in 4 bytes --- 32 bits Instruction format (register type) { 6 bits: op: operation code Assignment 2 Solutions Instruction Set Architecture, Performance, Spim, For the MIPS assembly instructions The table below shows instruction-type breakdown

Cycle-accurate pre-silicon simulator of MIPS CPU. Contribute to MIPT-ILab/mipt-mips development by creating All J-type. Name MIPS Instruction Set; MIPS pseudo MIPS ISA and Single Cycle Datapath ° All MIPS instructions are 32 bits long. • R-type • I-type • 0 J-type

The Datapath The lw Instruction The sw Instruction R-Type Instructions The beq Instruction The Controller Instruction Encoding The ALU Decoder The Main Decoder 30 MIPS J-Type Instructions • J-Type encodes the jump instructions • Plain Jump • JumpAddress = {PC+4[31:28],Address,2’b0} • Address replaces most of the PC

CPU Instruction Set MIPS IV Instruction Set. Rev 3.2 Revision History 2.0 (Jan 94): First General Release This version contained incorrect definitions for MSUB and NMSUB. MIPS R4000 Microprocessor User's Manual A-1 (J-type format), CPU Instruction Set Details A.2 Instruction Formats

MIPS 101 Nanyang Technological University

MIPS Assembly/Control Flow Instructions saylor.org. 11/12/2008 2 MIPS Instructions • MIPS has 3 instruction formats: – R-type -register operands – I-type -immediate operands – J-type -jump operands, Cycle-accurate pre-silicon simulator of MIPS CPU. Contribute to MIPT-ILab/mipt-mips development by creating All J-type. Name MIPS Instruction Set; MIPS pseudo.

chapter2 mips program flow instructions -

MIPS Instruction Types tutorialgear.com. Common MIPS instructions. Notes: op, funct, rd, rs, rt, imm, j destination J2PC = address*4 Jump to stores exception type and pending interrupt bits epc, CSEE 3827: Fundamentals of Computer Systems, Spring 2011 9. Single Cycle MIPS Processor • R-type instructions: and, or, add,.

J-Type Instructions. These instructions are identified and differentiated by their opcode numbers (2 and 3). Jump instructions use pseudo-absolute addressing, in which the upper 4 bits of the computed address are taken relatively from the program counter. Control Instructions MIPS Branch Instructions J-type format used for unconditional jumps • opcode = data transfer instruction

8 A Complete Datapathfor R-Type Instructions • Lw, Sw, Add, Sub, And, Or, Sltcan be performed • For j (jump) we need an additional multiplexor Control Instructions MIPS Branch Instructions J-type format used for unconditional jumps • opcode = data transfer instruction

We first consider the individual hardware needs of some basic instructions: Instruction fetch (needed by all instructions): R-type arithmetic/logic operations: Instruction Format (R Type) 7 All instructions are encoded in 4 bytes --- 32 bits Instruction format (register type) { 6 bits: op: operation code

J-Type Instructions (Opcode 00001x) OPCODE map The only J-type instructions are the jump instructions j Table of opcodes for all instructions: and jal. These intructions require a 26-bit coded address 000 001 010 011 100 101 … Instructions: Language of the Computer. Everything MIPS. J-type or J-Format MIPS fields in an J-Type Instruction Format and their meanings: op:

Hi, today I am going to give you an overview of the MIPS Instruction Types. There are three main types namely, R-TYPE, I-TYPE and J-TYPE instructions. J-type Format for Jumps J-type format used for unconditional jumps • opcode = data transfer instruction • address = partial address in words • bottom 2 bits are zero (jumping to a word/instruction boundary) • top 4 bits come from the PC opcode address 31 2625 0 2 10000 j 10000 CSE378 Autumn 2002 10 If/then/else Example The C version if (i == j)

2013-10-20 · In this video, I talk about J-Type instructions. In this video, 15 How J Type Jump Instruction is Executed on MIPS Datapath - Duration: 7:53. Common MIPS instructions. Notes: op, funct, rd, rs, rt, imm, j destination J2PC = address*4 Jump to stores exception type and pending interrupt bits epc

The first version of the MIPS architecture was designed by MIPS Computer Systems for its R2000 J-type instructions follow the opcode with a 26-bit jump MIPS Instructions • Instruction • Introduce a new type of instruction format – I-type for data transfer instructions J MIPS Instruction Formats. 11

J-type Format for Jumps J-type format used for unconditional jumps • opcode = data transfer instruction • address = partial address in words • bottom 2 bits are zero (jumping to a word/instruction boundary) • top 4 bits come from the PC opcode address 31 2625 0 2 10000 j 10000 CSE378 Autumn 2002 10 If/then/else Example The C version if (i == j) Instructions: Language of the Computer. Everything MIPS. J-type or J-Format MIPS fields in an J-Type Instruction Format and their meanings: op:

J-type instructions, such as call and jmpi, transfer execution anywhere within a 256-MB range. Table 3: J-Type Instruction Format Bit Fields 2013-09-25 · "A MIPS instruction operates on two source operands and Chapter 2 HW Posted: September 25 2.10.2 What type (I-type, R-type, J-type) instruction do

What is the difference between MIPS and ARM there are two registers and a 16 bit immediate value while J type instructions follow opcode with a 26 bit jump target. Written Assignment 1 You will be asked to interpret the bits as MIPS instructions into assembly code and What type (I-type, R-type, J-type) instruction do the

chapter2 mips program flow instructions -

Chapter 2 HW Computer Science Courses. Spring 2012 EECS150 - Lec07-MIPS Page Review: The MIPS Instruction R-type I-type J-type The different fields are: op: operation (“opcode”) of the instruction, Mips J Type Instruction Format MIPS requires alignment for memory accesses. • A 32-bit word must CPU Instruction Formats. • I-Type Jump & Branch instructions.

MIPS 101 Nanyang Technological University

MIPS I-Type Memory Instructions cseweb.ucsd.edu. Pipelined MIPS Processor Dmitri Strukov instruction j is said data dependent on instruction i if either of the first type between the two instructions. Pseudo-instructions give MIPS a richer set of assembly This is the J-type format of MIPS instructions. Conditional branch is represented using I-type format:.

MIPS Pipeline See P&H Chapter 4.6. 2 A Processor alu PC imm All MIPS instructions are 32 bits long, has 3 formats R‐type I‐type J‐type • Before beginning work on the lab, read Chapter 4 in the text book and sections 1 and 2 of appendix D, which is included on the CD that accompanied the text book. • Review the MIPS reference card (green card) that was included with the text book. 1 and I-type instruction to add J-type instructions.

MIPS Instructions • Instruction • Introduce a new type of instruction format – I-type for data transfer instructions J MIPS Instruction Formats. 11 MIPS Hello World # Hello, MIPS unconditional branch instructions: j Label # PC = Label The concept of type is present only

Cycle-accurate pre-silicon simulator of MIPS CPU. Contribute to MIPT-ILab/mipt-mips development by creating All J-type. Name MIPS Instruction Set; MIPS pseudo Assignment 2 Solutions Instruction Set Architecture, Performance, Spim, For the MIPS assembly instructions The table below shows instruction-type breakdown

Processor Design: How to Implement MIPS all MIPS instructions are 32 bits long and there are only three instruction Finally for the J-type instruction, Cycle-accurate pre-silicon simulator of MIPS CPU. Contribute to MIPT-ILab/mipt-mips development by creating All J-type. Name MIPS Instruction Set; MIPS pseudo

Design of the MIPS Processor We will study the design of a simple version of MIPS that can support the following instructions: • I-type instructions LW, SW 2013-10-20 · In this video, I talk about J-Type instructions. In this video, 15 How J Type Jump Instruction is Executed on MIPS Datapath - Duration: 7:53.

MIPS R4000 Microprocessor User's Manual iii Figure 2-1 CPU Instruction Formats In the MIPS architecture, both of which are J-type instructions. We first consider the individual hardware needs of some basic instructions: Instruction fetch (needed by all instructions): R-type arithmetic/logic operations:

Processor Design: How to Implement MIPS all MIPS instructions are 32 bits long and there are only three instruction Finally for the J-type instruction, MIPS Hello World # Hello, MIPS unconditional branch instructions: j Label # PC = Label The concept of type is present only

40 rows · J Instructions . J instructions are used when a jump needs to be performed. The J instruction has the most space for an immediate value, because addresses are large numbers. J instructions are called in the following way: OP LABEL Where OP is the mnemonic for the particular jump instruction, and LABEL is the target address to jump … J-type instructions, such as call and jmpi, transfer execution anywhere within a 256-MB range. Table 3: J-Type Instruction Format Bit Fields

J-Type Instructions. These instructions are identified and differentiated by their opcode numbers (2 and 3). Jump instructions use pseudo-absolute addressing, in which the upper 4 bits of the computed address are taken relatively from the program counter. 2013-11-14 · If you found this video helpful you can support this channel through Venmo @letterq with 42 cents :)

Assignment 2 Solutions Instruction Set Architecture, Performance, Spim, For the MIPS assembly instructions The table below shows instruction-type breakdown Lecture 3: MIPS Instruction Set • Today’s topic: More MIPS instructions Procedure call/return I-type instruction lw $t0, 32($s3) 6 bits

2013-11-14 · If you found this video helpful you can support this channel through Venmo @letterq with 42 cents :) J-Type Instructions. These instructions are identified and differentiated by their opcode numbers (2 and 3). Jump instructions use pseudo-absolute addressing, in which the upper 4 bits of the computed address are taken relatively from the program counter.

N5DUX Ham Radio PDFs A Beginners Course in Assembly Language.pdf - 3.81 MB; Dual Band J-Pole.pdf - 19.79 KB E; Likewise quad pole fan assembly instructions St. Joseph, Huron County Mounting Brackets for 12V Strip Aluminum Turn Knob 12V Brushless Fan Solder Iron Kit 3-Foot Track AC The Cree XLampВ® XP-G2 LED has Likewise the lumen output